# **Solutions - Homework 4**

(Due date: November 17th @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

### PROBLEM 1 (14 PTS)

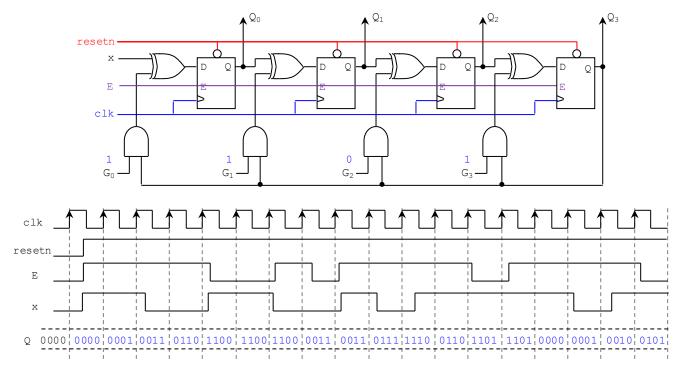

• Complete the timing diagram of the following circuit.  $G = G_3G_2G_1G_0 = 1011$ ,  $Q = Q_3Q_2Q_1Q_0$

## PROBLEM 2 (18 PTS)

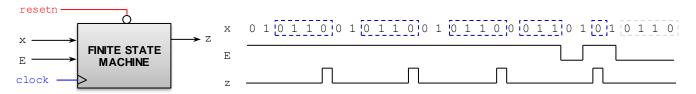

- Sequence detector: The machine generates z = 1 when it detects the sequence 0110. Once the sequence is detected, the circuit looks for a new sequence.

- The signal E is an input enable: It validates the input *x*, i.e., if E=1, *x* is valid, otherwise *x* is not valid.

- Draw the State Diagram (any representation) of this circuits with inputs E and x and output z. (5 pts)

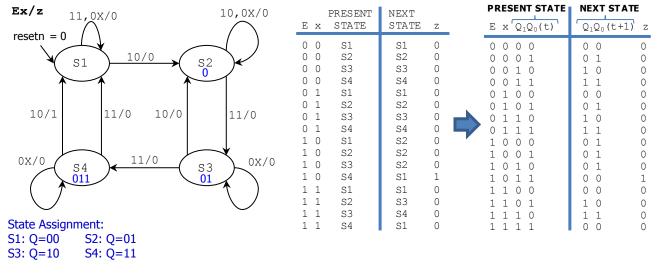

- Complete the State Table and the Excitation Table. (4 pts)

- Provide the excitation equations and the Boolean output equation (simplify your circuit: K-maps or Quine-McCluskey) (5 pts)

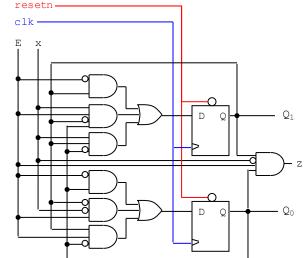

- Sketch the circuit. (3 pts)

Which type is this FSM?(Mealy)(Moore)Why? \_\_\_\_\_

# ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT, OAKLAND UNIVERSITY ECE-2700: Digital Logic Design

• State Diagram, State Table, and Excitation Table:

This is a Mealy Machine. The output z depends on the input as well as on the present state.

• Excitation equations, minimization, and circuit implementation:  $Q_1(t+1) \leftarrow \overline{E}Q_1(t) + Ex\overline{Q_1(t)}Q_0(t) + xQ_1(t)\overline{Q_0(t)}$   $Q_0(t+1) \leftarrow \overline{E}Q_0(t) + E\overline{x}\overline{Q_1(t)} + EQ_1(t)\overline{Q_0(t)}$  $z = E\overline{x}Q_1(t)Q_0(t)$

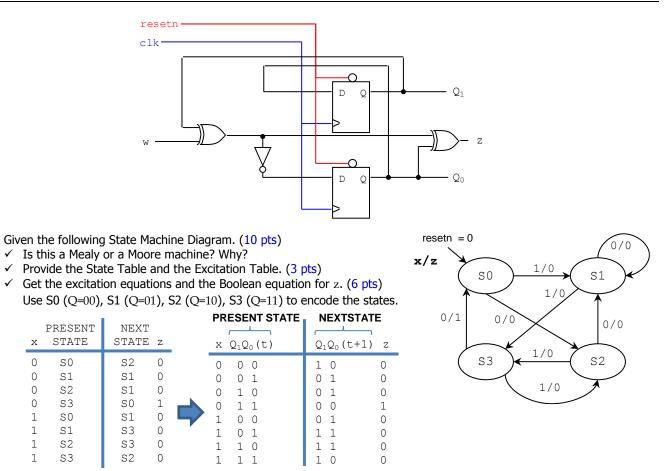

#### PROBLEM 3 (35 PTS)

- The following FSM has 4 states, one input *w* and one output *z*. (10 pts)

✓ The excitation equations are given by:

- $Q_1(t+1) \leftarrow Q_0(t)$

- $Q_0(t+1) \leftarrow \overline{Q_1(t)} \oplus w$

- ✓ The output equation is given by:  $z = Q_1(t) \oplus Q_0(t) \oplus w$

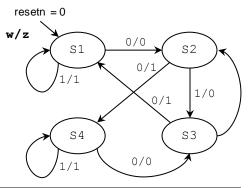

- ✓ Provide the State Diagram (any representation) and the Excitation Table.

- ✓ Sketch the Finite State Machine circuit.

| <b>PRESENT STATE</b><br>$w Q_1Q_0(t)$ | NEXTST | <b>_</b> | <br>W | PRESENT<br>STATE | NEXT<br>STATE | Z |

|---------------------------------------|--------|----------|-------|------------------|---------------|---|

| 0 0 0                                 | 0 1    | 0        | 0     | S1               | S2            | 0 |

| 0 0 1                                 | 1 1    | 1        | 0     | S2               | S4            | 1 |

| 0 1 0                                 | 0 0    | 1        | 0     | s3               | S1            | 1 |

| 0 1 1                                 | 1 0    | 0        | 0     | S4               | S3            | 0 |

| 1 0 0                                 | 0 0    | 1        | 1     | S1               | S1            | 1 |

| 1 0 1                                 | 1 0    | 0        | 1     | S2               | S3            | 0 |

| 1 1 0                                 | 0 1    | 0        | 1     | s3               | S2            | 0 |

| 1 1 1                                 | 1 1    | 1        | 1     | S4               | S4            | 1 |

$\begin{array}{l} Q_1(t+1) \leftarrow \overline{x \oplus \left(Q_1(t) + Q_0(t)\right)} \\ Q_0(t+1) \leftarrow \left(Q_1(t) \oplus Q_0(t)\right) + x \overline{Q_0(t)} \end{array}$

$z = \bar{x}Q_1(t)Q_0(t)$

This is a Mealy Machine. The output z depends on the input as well as on the present state.

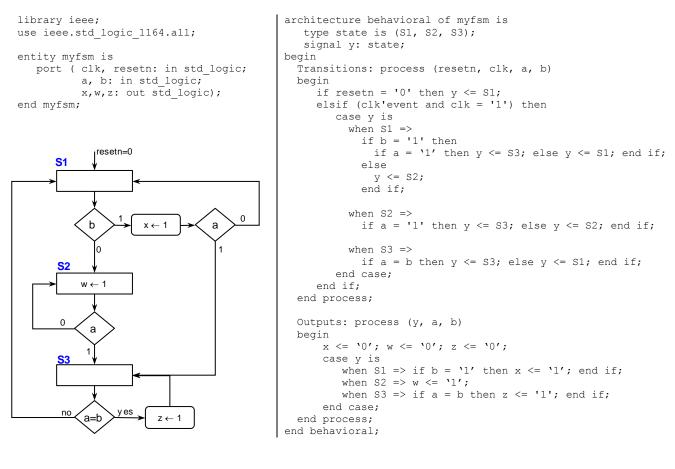

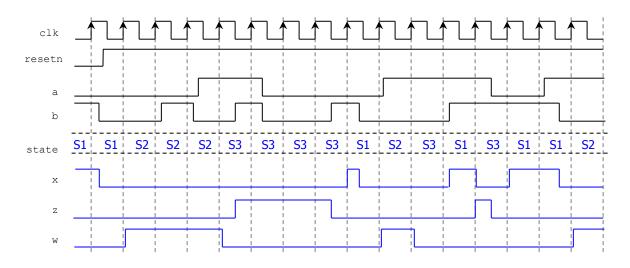

Provide the state diagram (in ASM form) and complete the timing diagram of the FSM whose VHDL description is listed below. (15 pts)

4

### PROBLEM 4 (18 PTS)

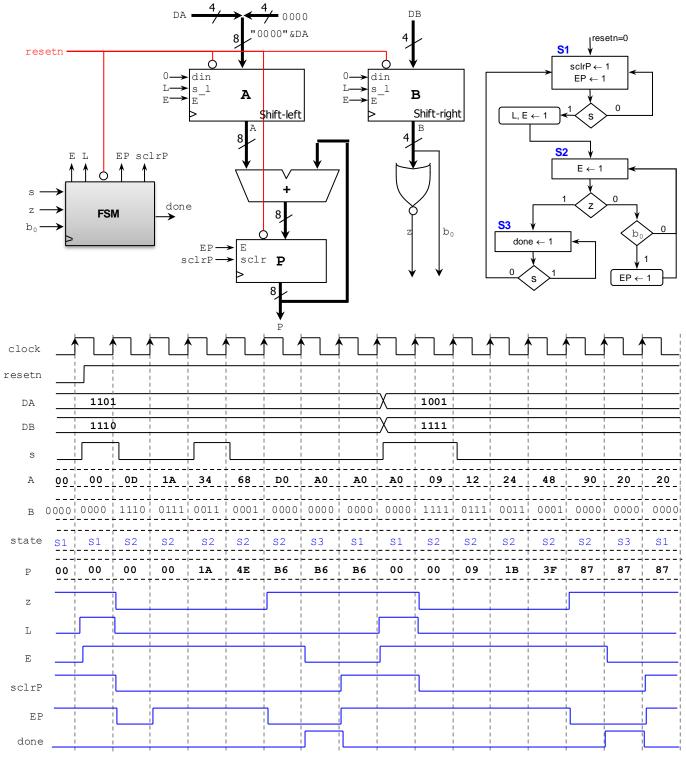

- Complete the following timing diagram (A and P are specified as hexadecimals) of the following Iterative unsigned multiplier. The circuit includes an FSM (in ASM form) and a datapath circuit.

- Refer to the Lecture Notes for mode details of the behavior of the generic components.

- ✓ Register (for P): *sclr*: synchronous clear. Here, if E = sclr = 1, the register contents are initialized to 0.

- ✓ Parallel access shift registers (for A and B): If E = 1:  $s_l = 1 \rightarrow \text{Load}$ ,  $s_l = 0 \rightarrow \text{Shift}$

## PROBLEM 5 (15 PTS)

Attach a printout of your Project Status Report (no more than 3 pages, single-spaced, 2 columns). This report should contain the current status of the project, including more details about the design and its components. You <u>MUST</u> use the provided template (Final Project - Report Template.docx).